今天我们将一起学习一下Cache一致性相关的内容。这部分的材料在网上并不多见,而且质量也差强人意。这次分享的公开资料是64-ia-32-architectures-optimization-manual。这份文档本来是Intel公开让用户调优系统的。但大家都知道,单纯对上层软件的调节是无法发挥系统的全部性能的。因此,很大程度的性能调优需要了解处理器的微架构和内部的Transaction Flow。而这份材料正好介绍了这些知识。除此之外,Mindshare的一本比较老的书也介绍Cache的架构以及Cache一致性相关的内容,这本书的名称是:Pentium Processor System Architecture。不过目前这本书不太好找,如果你有机会使用使用google books的话,上面可以预览阅读其中的章节。与今天我们分享内容有关的是其第四章:Multiple Processor and the MESI Model。

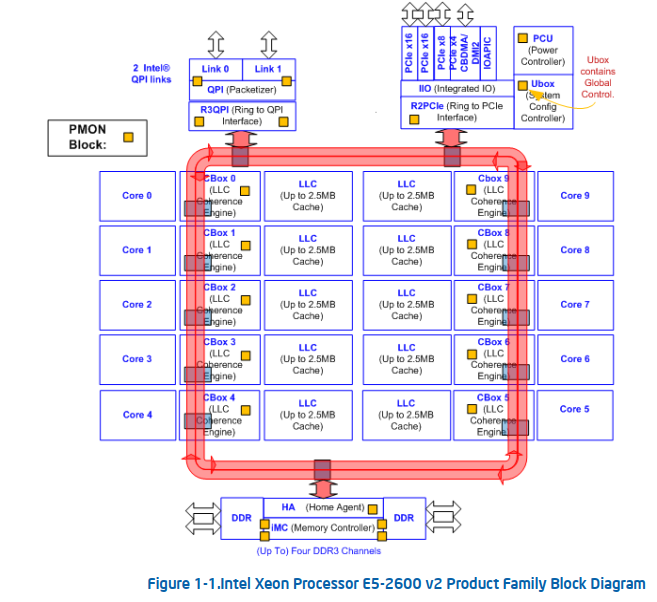

我们仍然以前面分享的Intel Xeon E5-2600 v2系统为例。

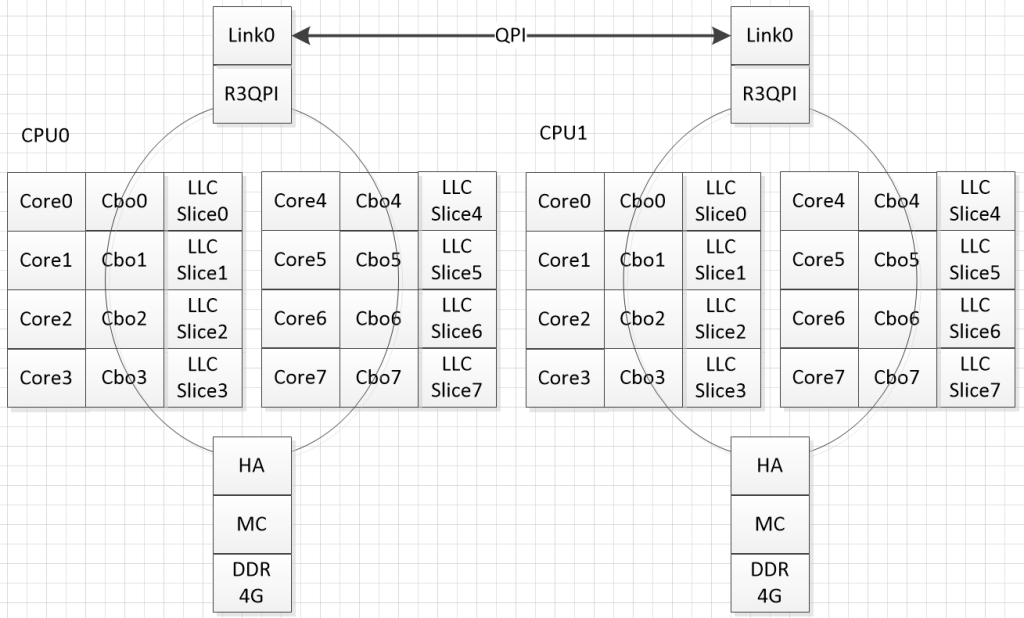

假设我们有一个2P的多处理器系统,每颗处理器中有8个core(核),一个Home Agent(HA),每个HA管辖一个Memory Controller(MC),每个MC下面有一根4G的内存。如下图所示:

我们首先思考一下,一个具体的Cacheline,最多有几份copy?

首先,我们来认识一下Cacheline,Cacheline从字面意思看就是存放在Cache中的某一条line,只不过这条line最初是存放在主存里的。因为Core可能需要经常使用而被缓存到离Core比较近的地方。根据距离Core的远近,Cache又被分为L1,L2,L3甚至L4 Cache,而这些Cache就是用来暂时存放Cacheline的地方。

其次,不同的处理器可能支持不同大小的Cacheline。例如,目前主流x86处理器的Cacheline Size都是64 Byte。即每次从主存移动到Cache中的数据块大小是64B。那么是不是Cache只缓存数据块内容就可以了呢?我们知道一个MOV指令可以从某个逻辑地址移动数据到处理器核的General Purpose寄存器中。当逻辑地址通过一定的手段转换成物理地址后,实际上处理器核会发起对某个物理地址的读访问。所以如果该物理地址对应的Cacheline正好在Cache中,那么处理器核就会很快的拿到资料。而问题刚好出现,处理器核通过什么询问Cache索要资料呢?不难看出,处理器核手上有需要访问数据的物理地址。所以如果Cache里都是一些64B的数据的话,Cache又怎么知道这些数据对应的地址是什么呢?因此,Cache不但要缓存数据,同时要缓存该数据所对应的物理地址的信息。那么这笔Cacheline如果存放在主存中,需要同时存放物理地址吗?答案是不需要的,因为所有的内存空间都会安排物理地址与之对应。除了内存镜像功能以外,任何指向主存的物理地址都有唯一的内存空间与之对应。如果一个系统中有两个内存空间对应同一个物理地址的时候,在写操作的时候,系统就不知道应该把数据写到哪个内存空间去了。(镜像的时候是同时写两个地方)

回到我们最开始的问题,一个具体的Cacheline,最多有几份copy?那么在主存侧,如果该Cacheline不在内存镜像区的话,那么整个系统中将只会有一份copy。接下来,我们考虑一下在Cache中,最多会有几份?根据前面的假设,一颗处理器中有8个core,8片LLC,那么是不是在一颗处理器中的LLC中,最多有8份呢?答案是否定的。如果不开NUMA的话,整个处理器就是一个NUMA域,这个NUMA域中的所有LLC为所有处理器核共享。所以答案是只会有一份。那8片LLC是做到共享的呢?根据我们前面文章的介绍,当一个处理器核发起对某个物理地址的访问的时候,处理器核会通过某种HASH算法,计算出该物理地址属于哪个Cbo负责,然后处理器核把请求发给那个目标Cbo,Cbo负责查询它身后的那片LLC。因此不存在某个具体的物理地址通过HASH算法后,既属于Cbo0又属于Cbo1的情况。换句话说,系统地址空间被这8个Cbo分光了,而且分配方法是固定的。

我们打个比方来说明这个问题。假设一间医院的取药处,分为中药,西药,外用药三个区,这三个区将医生所有的用药种类都分光了。那么当医生开了一种药后,根据条码我得知这种要究竟是要去哪个取药区去领取,而不会是某种药既可能在西药区又可能在外用药区。当某个药在西药区取不到的时候,西药区的医生要去库房取,而不会到中药区或外用药区去取药。这个和我们的L3 Cache系统还是很相似的。

根据上述的描述,一个2P系统中有两个处理器,每个处理器是一个独立的NUMA域,那么对于某一具体的Cacheline,每个处理器都将有一个固定的Cbo负责,通常该Cbo的号码都会一致,因为HASH算法与Cbo的数量相关。那么在L3 Cache中,一个2P系统将最多有两份Copy,一份在CPU0的某个Cbo身后的LLC中,另一份在CPU1的相同号码的Cbo身后。

在之前的文章中我们介绍过,L1和L2都为某个Core独享并处于Core的内部。而且L2包含(Inclusive)了L1,即任意一笔Cacheline如果在L1中,那么它必定在L2中。所以,对于某个Core的来说,一笔数据类型的Cacheline,最多会有两份,一份在L1D中,一份在L2中。如果一个处理器有8个核,那么将会最多有16份Copy。

好了,究竟在一个8核处理器的2P系统中,一笔Cacheline最多会有多少份Copy,你算出来了吗?

参考资料:

Reference:

Intel® Xeon® Processor E5 v2 and E7 v2 Product Families Uncore Performance Monitoring Reference Manual

Intel® 64 and IA-32 Architectures Optimization Reference Manual

Intel® 64 and IA-32 Architectures Software Developer’s Manual